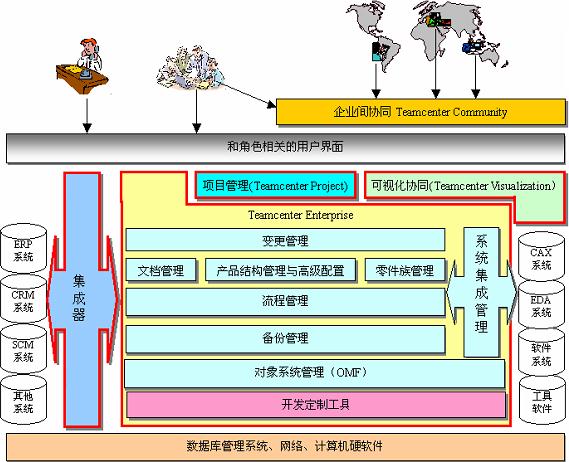

����Ʒ�з���������ս֮һ����α�֤���������������̵IJ�ͬ��֮������ת��ʱ����ȷ�Ժ������ԡ�

��ͳ�ϣ����ʦ��һֱ���á��ֶ���֮���ķ�������ÿ����ʹ�ò�ͬ����ƹ��ߺ����ݼ��������������Ҫ��һ����ת�Ƶ���һ����ʱ�������ԭ��ͼ ��Ƶ�PCB���ߣ�ͨ����ҪһЩ�����ļ������ǽ���IJ�Ʒ��Ʋ���������ԭ��ͼ��PCB���ߣ���Ʒ�з������˰弶��ơ�Ƕ��ʽ����������FPGA��ơ��� еCAD(MCAD)�����ʲɹ�ֱ���������������һϵ�й��̡�����ڶ�Ĺ�����Ҫ�����IJ�ͬ��ʽ�Ĺ����ļ���Ҫ����Щ�ļ����а汾��������֤���ظ��Ժ� ���ԣ�������������Ŀ����������һ��ج�Σ�ͬ��Ҳ����֤�����������ش������ȷ�ԣ��Ӷ���Ϊ�����ƹ���������Ҫ�Ĵ�����Դ��

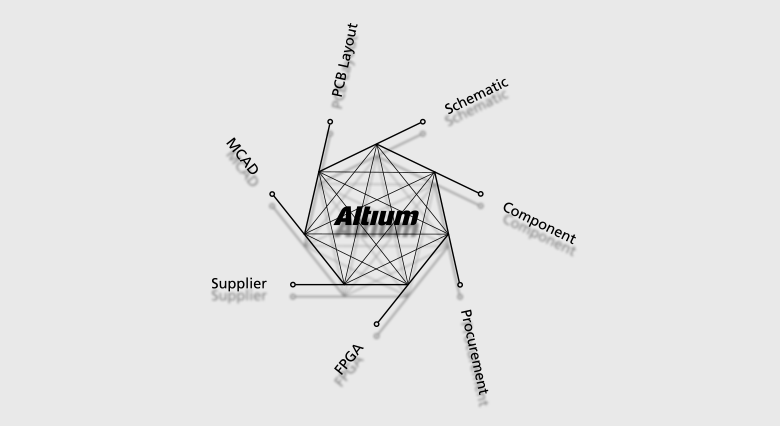

Altium Designer���������֡��ֶ���֮���ķ�����������һ�ֻ�������ƻ����ġ�ͳһ����ģ�͡���Ӧ�Դ�ͳģʽ�����������⡣

ͳһ����ģ��

Altium Designer����ƹ���Χ��һ��λ�����ĵ�ͳһ����ģ�ͣ�ÿ����ƹ��߶�ֱ���������һ�����ݼ����н�����

ͳһ����ģ�Ͳ�����ָһ���ļ����������е�������ݣ������ڲ�ͬ����������ظ����á��෴����ÿ���������ƹ���ʱ���ù��ߴӱ����������ļ� ������ֻ�뱾������ص��Dz������ݡ���ִ�к�̨���������룩֮���ⲿ�����ݱ����ɵ�λ�ڼ�����洢���е�ͳһ����ģ���С�ÿһ���������Ĺ���ֻ�༭�� ά��ͳһ����ģ�������䱾����صIJ��֡������б������ʱ��ÿ���������Ĺ��ߴ�ͳһ����ģ���б������Լ���ص����ݵ�Ӳ���С�

ͳһ����ģ�͵��ŵ㣺

1.�ڲ�ͬ���������ֱ�ӽ�������ͬ��������Ҫ�����ļ�

2.ÿһλ���ʦ�����Կ�������������ģ�ͣ����Է����κ������Ϣ�Ա��������õľ���

3.������ݵ�״̬�����ױ���֤����֤����Ч�ذ汾���ƺ��ļ�����

ֱ�����ͬ��

Altium Designer���еĹ��߲���������ͳһ����ģ�ͣ�������ݸı�ʱ����һ����ƽε���һ����ƽε����̼�ֱ�ӣ����Ҳ������������ԭ��ͼ������һ ���µ�Ԫ���������и�������µ�Ԫ�������������PCB�еȴ����á�����һ��1000�����ŵ�FPGA�Ͻ������Ž����Ա��ڸ��õ�����ʱ����Щ�µ����� ���佫��ֱ�ӷ��ص�FPGA����У���ִ����һ�ֵIJ��ֺͲ��ߡ���ΪFPGA�����˴��������(soft-processor)���Ӹ���Ĵ洢�ռ�ʱ���� Щ�仯�᷵�ص�Ƕ��ʽ��EMB����Ŀ�У��û���ֱ�Ӷ������±��롣

�ɴ˿��Կ�����ԭ����Ŀ���߳������ڳ������������ڱ�ü�����

��Ŀ�����ȱ�֤�����õľ���

�������ƶ����ŶӺ����Ľ�������ŶӺ���������ս֮һ������α�֤�Ŷ��е�ÿλ��Ա���ܹ���ȫ�˽ǰ�����״̬��

�ȷ�˵�弶����ʦ����ͨ������FPGA�����Ž�ʡ����PCB���ߣ���ô����FPGA����ʦ���ԣ���Ҫ���̵õ������Ϣ��ȥ���FPGA���Ž���֮���Ƿ���Ȼ���Ժ�����ɲ��ֺͲ��ߡ��Ƿ�������������Ҫ�����ʱҪ�����Ƿdz���Ҫ�ġ�

ʹ��ͳһ����ģ�ͱ�֤���Ŷ��е�ÿλ��Աÿʱÿ�̶���������˽ǰ����Ŀ���״̬��