ЭЈЙ§АбЧЖШыЪНCДњТыЧЈШыЕНПьЫйПЩБрГЬгВМўгЩДЫЛёЕУадФмЕФМЋДѓЬсЩ§ЃЌетЪЧдкЮвУЧЕФЩшМЦжаЪЙгУFPGAЕФвЛИіжївЊгХЪЦЁЃ

Altium DesignerЕФЭГвЛЩшМЦЛЗОГЃЌЭЈЙ§жЧФмЕФЁЂМђЕЅвзгУЕФгУЁАCЕНгВМўЁБММЪѕЃЌЪЙЕУШэМўЩшМЦКЭПЩБрГЬгВМўЩшМЦНєУмСЊЯЕдквЛЦ№ЁЃжЛашвЊдкДњТыжабЁШЁФмЙЛЕУвц гкгВМўМгЫйЕФЙІФмКЭЫуЗЈЃЌШУAltium DesignerЕФЁАCЕНгВМўЁББрвыЦїздЖЏЕиЩњГЩЫљвЊЧѓЕФгВМўЪЕЯжЁЃ

Altium DesignerЫљОпгаЕФСэЭтвЛИіЧПДѓЬиЕуОЭЪЧЫќФмЙЛГфЗжРћгУFPGAЕФЧБСІЁЃ

ВЛвЊЧѓHDLОбщ

ЪЙгУAltium DesignerЃЌРћгУCДњТыБрГЬЪЕЯжгВМўМгЫйВЂВЛвЊЧѓHDLММФмЁЃ

Altium DesignerЕФЁАCЕНгВМўЁББрвыЦїжБНгДгБъзМCДњТыВњЩњзлКЯЕФгВМўЁЃИпЫйВЂааЕФгВМўНЋвджЛЯрЕБгкЖдЕШШэМўЕФМИЗжжЎвЛЕФЪБжгжмЦкЫйЖШдЫааЃЌФуЕФЩшМЦЕФадФмКЭаЇТЪЖМЕУвдЬсЩ§ЁЃ

гВМўМгЫй

аэЖрМЦЫуТпМЫуЗЈЃЌжБНгдкШэМўжаБрТыКЭЕїЪдЃЌЖјЧвБЛДЎаажДааЃЌЕЋЪЧЫќУЧЕФФкдкЪЧВЂааЕФ ЈC Р§ШчМгУмЫуЗЈКЭаХКХДІРэЁЃAltium designer дЪаэФуАбетаЉЙІФмИФГЩВЂаагВМўВйзїЃЌвдБуФуФмГфЗжРћгУУПвЛИіПЩгУзЪдДЁЃ

Altium DesignerЕФЯШНјЁАCЕНгВМўЁББрвыЦїНЛИЖЕФгВМўМгЫйЃЌВЩгУБъзМЕФЗЧЪБађЕФISO ЈC CдДДњТыЃЌВњЩњFPGAЕФгВМўРДЪЕЯжЫљашЕФЙІФмЁЃЮвУЧВЛашвЊШЅДІРэHDLЃЌЯЕЭГЛсВњЩњзлКЯЕФЁЂЗТецОЭаїЕФHDLгяОфЁЃ

ЬНЫїбЁЯю

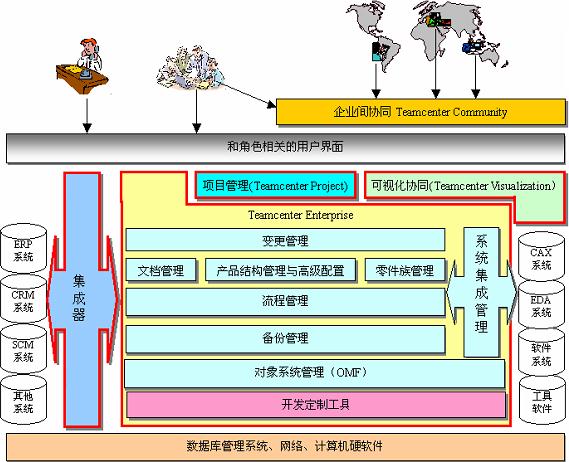

Altium DesignerжаЁАCЕНгВМўЁБДІРэЙ§ГЬЕФСщЛюЪЕЯжЃЌШУЮвУЧгаЛњЛсРДВтЪдКЭЬНЫїАбШэМўЙІФмзЊвЦЕНFPGAгВМўНсЙЙЫљДјРДЕФКУДІЁЃ

ЪЪЕБЕФгВМўМгЫйЙІФмПЩжБНгдкдДДњТыМЖБЛЪЖБ№ЃЌгыДЫЭЌЪБAltium DesignerвВЬсЙЉвЛИіМђЕЅЖјжБЙлЕФНчУцЃЌПЩвдСщЛюЕибЁдёКЭШЅГ§ФЧаЉвдгВМўаЮЪНдЫааЕФЙІФмЁЃЫљгаЕФШэМўКЭгВМўАцБОЭЌЪБДцдкЃЌЮвУЧПЩвдДгвЛИіЧаЛЛЕНСэвЛИіЃЌШЛКѓжиаТБрвыЩшМЦРДЦРЙРНсЙћЁЃ

ИпМЖЩшМЦНчУц

Altium DesignerжаАќКЌСЫгВМўЙІФмДњТызїЮЊзЈгУДІРэЦїЃЈASPЃЉЃЌЖјВЛЪЧВњЩњвЛИіВЛФмЗУЮЪЕФHDLЁАгВПщЁБ- ЫфЫЕЫќДњБэСЫФуЕФгВМўМгЫйЁЃ

ASPЪЧвЛИідкFPGAЩшМЦжаПЩЙмРэЕФКЭПЩХфжУЕФЦїМўЃЌОЭЯёЦфЫћШЮКЮЦїМўвЛбљЁЃ Altium DesignerЬсЙЉСЫУцЯђИпМЖдРэЭМКЭOpenBus FPGAЩшМЦЕФWishboneзмЯпЕФзЈУХASPЃЌШУЁАОЋУїгВМўЁБЕФШэМўПЊЗЂШЫдБЭъШЋПижЦЧЖШыЪНгІгУГЬађЕФПЊЗЂЁЃ